Общие сведения[]

В эту группу вошли регистры, не вошедшие формально в блок управления системой (SCB), но выполняющие подобные ему функции по управлению процессором и прерываниями.

Доступ к этим регистрам возможен только для привилегированного кода и только выровненными словами. Исключением является регистр STIR, доступ к которому может быть разрешён для непривилегированного кода.

Список регистров приведён в следующей таблице.

| Адрес | Обозначение | Доступ | Значение после сброса | Описание |

|---|---|---|---|---|

| E000E000 | Главный регистр управления, зарезервирован | |||

| E000E004 | Регистр типа контроллера прерываний | |||

| E000E008 | Вспомогательный регистр управления | |||

| E000E00C | Регистр управления питанием сопроцессоров | |||

| E000EF00 | Регистр программного запроса прерываний | |||

| E000EF04 E000EF4C |

Зарезервированы. | |||

| E000EF50 | Регистр инвалидации кэша команд в Cortex-M7. | |||

| E000EF54 E000EF5C |

Зарезервированы. | |||

| E000EF60 | Регистр обслуживания кэша данных в Cortex-M7 | |||

| E000EF64 E000EF8C |

Зарезервировано | |||

| E000EF90 E000EFCC |

Определяются реализацией. | |||

| E000EFD0 | Регистр идентификации периферии 4. | |||

| E000EFD4 | Регистр идентификации периферии 5. | |||

| E000EFD8 | Регистр идентификации периферии 6. | |||

| E000EFDC | Регистр идентификации периферии 7. | |||

| E000EFE0 | Регистр идентификации периферии 0. | |||

| E000EFE4 | Регистр идентификации периферии 1. | |||

| E000EFE8 | Регистр идентификации периферии 2. | |||

| E000EFEC | Регистр идентификации периферии 3. | |||

| E000EFF0 | Регистр идентификации компонентов 0. | |||

| E000EFF4 | Регистр идентификации компонентов 1. | |||

| E000EFF8 | Регистр идентификации компонентов 2. | |||

| E000EFFC | Регистр идентификации компонентов 3. |

Описание регистров[]

Регистр типа контроллера прерываний ICTR[]

Адрес: E000E004.

Доступ: только чтение, только слово, привилегированный.

Начиная с ARMv8.1-M, доступность регистра для непривилегированных отладочных доступов при установленном бите DAUTHCTRL_S.UIDAPEN или DAUTHCTRL_NS.UIDAPEN определяется реализацией.

Наличие: отсутствует в ARMv6-M, всегда имеется в ARMv7-M и ARMv8-M.

Безопасность (ARMv8-M): безопасное ПО может обратиться к небезопасной версии регистра по адресу E002E004. Для небезопасного ПО и отладчика по последнему адресу всегда считывается нуль.

Регистр не имеет отдельных версий для разных состояний безопасности.

| Разряды | Доступ | Обозначение | Функция |

|---|---|---|---|

| Зарезервированы. | |||

| Общее число линий прерываний, поддерживаемое данной реализацией, заданное группами по 32. Число линий равно 32 * (INTLINESNUM + 1). Для ARMv7-M оговаривается, что значение 1111 соответствует максимально возможному числу линий — 496. |

Вспомогательный регистр управления ACTLR[]

Адрес: E000E008.

Доступ: в ARMv6-M и ARMv7-M определяется реализацией; в ARMv8-M – только привилегированный, полным словом.

Начиная с ARMv8.1-M, реализация определяет, будет ли игнорироваться отладочная запись при работающем процессоре.

Наличие: всегда.

Безопасность (ARMv8-M): безопасное ПО может обратиться к небезопасной версии регистра по адресу E002E008. Для небезопасного ПО и отладчика по последнему адресу всегда считывается нуль.

Наличие отдельных версий для разных состояний безопасности определяется реализацией.

Назначение разрядов этого регистра определяется реализацией. Несколько известных вариантов приведено ниже.

Формат ACTLR для процессорных ядер Cortex-M0 и Cortex-M0+[]

Ядра Cortex-M0 и Cortex-M0+ фактически не содержат регистр ACTRL: любая запись по его адресу игнорируется, а чтение возвращает нули.

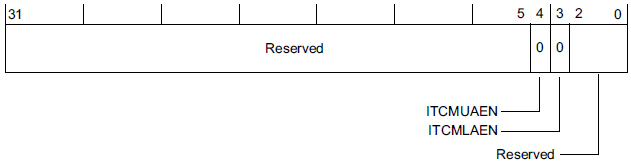

Формат ACTLR для процессорного ядра Cortex-M1[]

| Разряды | Доступ | Обозначение | Функция |

|---|---|---|---|

| Зарезервированы. | |||

|

Управление доступом к тесно связанной памяти команд (ITCM) через верхнюю область адресов (начиная с адреса 10000000):

При сбросе устанавливается равным состоянию соответствующего конфигурационного входа процессорного ядра. | |||

|

Управление доступом к ITCM через нижнюю область адресов (начиная с адреса 00000000):

При сбросе устанавливается равным состоянию соответствующего конфигурационного входа процессорного ядра. | |||

| Зарезервированы. |

Когда бит ITCMUAEN или ITCMLAEN установлен, обращения процессора по адресам, попадающим в соответствующий диапазон ITCM,вызывают доступы к ITCM. Когда бит сброшен, обращения по тем же адресам передаются на внешнюю шину. Таким образом, потенциально одним и тем же адресам могут соответствовать ячейки памяти как в ITCM, так и в памяти, доступной через внешнюю шину.

Формат ACTLR для процессорного ядра Cortex-M3[]

В ядре Cortex-M3 регистр ACTLR позволяет при необходимости отключить определённые особенности выполнения команд, призванные повысить производительность. При сбросе все они разрешены, а содержимое регистра равно нулю.

Приведённая информация относится к версии r2p0. TRM для версии r2p1 воспроизводит в этой и ряде других частей TRM на ядро Cortex-M4, что, очевидно, является ошибкой; по всей вероятности, ACTLR в r2p1 не отличается от r2p0. В более ранних ядрах отсутствует как минимум бит DISDEFWBUF, упоминаемый в списке ошибок (см. ошибку 838469).

| Разряды | Доступ | Обозначение | Функция |

|---|---|---|---|

| Зарезервированы. | |||

|

Запрет сворачивания команды IT, т. е. начала выполнения первой команды в блоке IT в то время, когда выполнение самой команды IT ещё не завершено. Сворачивание должно быть запрещено, если необходимо обеспечить время выполнения IT-блоков с точностью до такта, поскольку при разрешённом сворачивании оно может колебаться. | |||

|

Запрет использования буфера записи, т. е. обеспечение завершения записи в память до начала выполнения следующей команды. Может быть полезно при отладке, поскольку отказы шины (прерывания BusFault) при включенном буфере записи могут быть неточными, а при выключенном будут точными. | |||

|

Запрет прерывания многотактовых команд. Этот запрет потенциально увеличивает время реакции на прерывания, поскольку запрещает прерывание выполнения таких команд, как LDM и STM. |

Формат ACTLR для процессорного ядра Cortex-M4[]

В ядре Cortex-M4 регистр ACTLR позволяет при необходимости отключить определённые особенности выполнения команд, призванные повысить производительность. При сбросе все они разрешены, а содержимое регистра равно нулю.

| Разряды | Доступ | Обозначение | Функция |

|---|---|---|---|

| Зарезервированы. | |||

|

Запрет завершения команд с плавающей запятой вне очереди по отношению к целочисленным командам. | |||

|

Запрет автоматического обновления бита CONTROL.FPCA. При записи в регистр значение этого бита не должно изменяться или же он может быть сброшен, но не установлен (т. е., по сути, запретить автоматическое обновление бита CONTROL.FPCA нельзя). | |||

| Зарезервированы. | |||

|

Запрет сворачивания команды IT, т. е. начала выполнения первой команды в блоке IT в то время, когда выполнение самой команды IT ещё не завершено. Сворачивание должно быть запрещено, если необходимо обеспечить время выполнения IT-блоков с точностью до такта, поскольку при разрешённом сворачивании оно может колебаться. | |||

|

Запрет использования буфера записи, т. е. обеспечение завершения записи в память до начала выполнения следующей команды. Может быть полезно при отладке, поскольку отказы шины (прерывания BusFault) при включенном буфере записи могут быть неточными, а при выключенном будут точными. | |||

|

Запрет прерывания многотактовых команд. Этот запрет потенциально увеличивает время реакции на прерывания, поскольку запрещает прерывание выполнения таких команд, как LDM и STM. |

Формат ACTLR для процессорного ядра Cortex-M7[]

В ядре Cortex-M7 регистр ACTLR позволяет при необходимости отключить определённые особенности выполнения команд, призванные повысить производительность. При сбросе все они разрешены.

| Разряды | Доступ | Обозначение | Функция |

|---|---|---|---|

| Зарезервированы. | |||

|

В документации функции бита не указаны; судя по его обозначению, в состоянии 1 он запрещает некие оптимизации при запуске команд FPU на выполнение. | |||

|

Запрет критических операций «чтения под записью» на шине AXI:

| |||

|

Запрет динамического назначения для команд сложения и вычитания. Когда установлен, все такие команды выполняются на одном исполнительном блоке (EX2); когда сброшен, некоторые команды могут выполняться на EX1. | |||

|

Маска команд, которые не могут быть запущены в канале 1:

| |||

|

Маска видов команд в канале 0, запрещающих инициирование двух команд:

| |||

|

Запрет критического «чтения под чтением» на шине AXI. Когда установлен, считывание из памяти устройства или строго упорядоченной памяти, а также эксклюзивное считывание разделяемой памяти не начинается, пока все уже выполняющиеся на AXI операции считывания не будут завершены. | |||

|

Запрет добавления новых элементов в кэш адресов переходов. Уже имеющиеся элементы могут обновляться, как обычно. | |||

|

Запрет использования кэша адресов переходов; работает только статический предсказатель ветвлений. | |||

|

Запрет опорожнения ATB в ITM и DWT. Этот бит жёстко установлен. | |||

|

Запрет динамического выделения при чтении для областей памяти с обратной записью и выделением при чтении. | |||

|

Запрет выдачи исключений GPU. | |||

| Зарезервированы. | |||

|

Назначение бита не описано; судя по названию, запрещает «свёртку» команд. | |||

| Зарезервированы. |

Формат ACTLR для процессорного ядра Cortex-M23[]

| Разряды | Доступ | Обозначение | Функция |

|---|---|---|---|

| Зарезервированы. | |||

При наличии расширения безопасности этот бит имеет независимые версии для безопасного и небезопасного режимов. | |||

| Зарезервированы. |

Формат ACTLR для процессорного ядра Cortex-M33[]

Формат вспомогательного регистра управления для ядра Cortex-M33

| Разряды | Доступ | Обозначение | Функция |

|---|---|---|---|

| Зарезервированы. | |||

При наличии расширения безопасности этот бит имеет независимые версии для безопасного и небезопасного режимов. | |||

| Зарезервированы. | |||

|

Устанавливается при использовании STL (библиотека тестирования ПО); по завершении использования STL сбрасывается. | |||

|

Когда установлен, запрещает опорожнение ITM/DWT ATB. | |||

| Зарезервирован. | |||

|

Когда установлен, запрещает выход запроса прерывания от FPU. | |||

|

Когда установлен, запрещает внеочередное завершение команд с плавающей запятой по отношению к остальным командам. | |||

| Зарезервированы. | |||

|

Когда установлен, запрещает запуск двух команд за такт. | |||

| Зарезервирован. | |||

|

Когда установлен, запрещает прерывание выполнения многотактовых команд. |

Формат ACTLR для процессорного ядра Cortex-M55[]

| Разряды | Доступ | Обозначение | Функция |

|---|---|---|---|

| Зарезервированы. | |||

|

Когда установлен, считывание из памяти устройства или эксклюзивное считывание из разделяемой памяти на шине AXI не начинается, пока все ранее начатые операции записи не будут завершены. | |||

| Зарезервированы. | |||

|

Запрещает те или иные возможности одновременного запуска двух команд:

| |||

|

Когда установлен, считывание из памяти устройства или эксклюзивное считывание из разделяемой памяти на шине AXI не начинается, пока все ранее начатые операции считывания не будут завершены. | |||

| Зарезервированы. | |||

|

Когда установлен, запрещает опорожнение ITM/DWT ATB. | |||

|

Когда установлен, запрещает выделение кэш-памяти при записи. | |||

|

Когда установлен, запрещает выход запроса прерывания от FPU. | |||

| Зарезервированы. | |||

|

Запрещает совмещение при выполнении команд. | |||

|

Запрещает совмещение скалярных команд. | |||

| Зарезервирован. | |||

|

Запрещает циклы с малыми накладными расходами. | |||

|

Запрещает предсказание циклов с малыми накладными расходами. | |||

|

Когда установлен, запрещает запуск двух команд за такт. | |||

| Зарезервированы. |

Регистр управления питанием сопроцессоров CPPWR[]

Адрес: E000E00C.

Доступ: только привилегированный, полным словом.

Начиная с версии ARMv8.1-M, отладочная запись в этот регистр при работающем процессоре может игнорироваться, что определяется реализацией.

Наличие: только ARMv8-M с основным расширением.

Безопасность (ARMv8-M): безопасное ПО может обратиться к небезопасной версии регистра по адресу E002E00C. Для небезопасного ПО и отладчика по последнему адресу всегда считывается нуль.

Регистр не имеет отдельных версий для разных состояний безопасности.

| Разряды | Доступ | Обозначение | Функция |

|---|---|---|---|

| Зарезервированы. | |||

|

Этот разряд доступен только в безопасном состоянии и должен программироваться в состояние, совпадающее с состоянием бита SUS10 (см. ниже), в противном случае его итоговое значение неизвестно. Само по себе оно игнорируется. | |||

|

Этот разряд должен программироваться в состояние, совпадающее с состоянием бита SU10 (см. ниже), в противном случае его итоговое значение неизвестно. Само по себе оно игнорируется. | |||

|

Этот разряд определяет доступность бита SU10 из небезопасного состояния:

Если SU10 не реализован, то SUS10 также не реализован. | |||

|

Этот разряд определяет, разрешено ли FPU и MVE переходить в неизвестное состояние:

Технически установленное значение этого бита разрешает полностью отключать электропитание FPU и MVE. | |||

| Зарезервированы. | |||

|

Эти биты доступны только в безопасном режиме и управляют доступностью соответствующих битов SU7:0 из небезопасного режима:

Если некоторый бит SU не реализован, соответствующий бит SUS также не реализован. | |||

|

Эти биты определяют, должен ли соответствующий сопроцессор сохранять известное состояние:

Технически эти биты управляют возможностью отключения электропитания соответствующих сопроцессоров. |

Хотя в документации это и не сказано явно, биты SUS отсутствуют (всегда равны нулю), если процессор не имеет расширения безопасности.

Регистр программного запроса прерываний STIR[]

Адрес: E000EF00.

Доступ: только запись; может быть разрешён доступ для непривилегированного кода (см. бит CCR.USERSETMPEND). Не имеет отдельных версий для разных режимов безопасности.

Наличие: только ARMv8-M с основным расширением и ARMv7-M.

| Разряды | Доступ | Обозначение | Функция |

|---|---|---|---|

| Зарезервированы. | |||

|

Задаёт номер прерывания, которое должно быть выдано. Записываемая сюда величина равна номеру соответствующего прерывания минус 16, т. е. стандартные архитектурные прерывания (HardFault и т. д.) вызвать с помощью этого механизма нельзя. |