Общие сведения[]

Блок управления системой (SCB, system control block), являющийся частью пространства управления системой (SCS), содержит большую часть регистров, управляющих работой собственно процессора. Кроме них, для управления используются ещё несколько регистров, входящих прямо в состав процессорного ядра, и ряд других регистров SCS.

Регистры SCB, как и все регистры на шине PPB, используют порядок следования байтов «младший-старший» независимо от порядка следования байтов в остальной части системы. Если в описании регистра прямо не сказано иное, доступ к нему возможен только для привилегированного кода и только выровненным полным словом. Попытка доступа меньшей ширины либо невыровненного доступа приведёт к непредсказуемым последствиям, попытка обращения к регистру со стороны непривилегированного кода вызовет отказ UsageFault или HardFault.

При наличии расширения безопасности некоторые регистры целиком или отдельные биты регистров могут иметь отдельные экземпляры для безопасного и небезопасного режимов работы; наличие отдельных вариантов указывается в описании регистра явным образом. Адрес регистра, приводимый в его описании, обеспечивает доступ к варианту этого регистра, соответствующему текущему активному режиму безопасности (т. е. к безопасной версии регистра, если процессор работает в безопасном режиме, и к небезопасной версии в небезопасном режиме). Из безопасного кода можно получить доступ к регистрам небезопасного режима с помощью адресов, численно на 00020000 большими, чем основные адреса; попытка небезопасного кода обратиться по таким адресам для записи игнорируется, а при чтении возвращает нули. В тех случаях, когда необходимо указать не только регистр, но и его версию безопасности, к его имени добавляется суффикс _S или _NS для безопасного и небезопасного режимов соответственно.

Возможности доступа отладчика к регистрам зависят от режима безопасности и от состояния некоторых битов, контролирующих возможности отладки.

Перечень всех регистров SCB приведён в следующей таблице, а их подробные описания даны ниже в соответствующих подразделах.

Примечания. 1. Начальное значение регистра VTOR определяется реализацией.

2. Относительно начального состояния регистра AIRCR документация противоречива. С одной стороны, для ARMv8-M указывается, что после тёплого сброса все его биты, кроме 15, равны нулю, а значение бита 15 определяется реализацией, так как оно показывает порядок следования байтов. С другой стороны, это же руководство утверждает, что 1) при отсутствии расширения безопасности бит 13 считывается как единица (в более ранних версиях архитектуры он зарезервирован и равен нулю); 2) бит 5 показывает, используется ли неявный ESB, причём его использование или неиспользование может быть жёстко сконфигурировано (и бит тогда доступен только для чтения); 3) бит 4 указывает, зависит ли время выполнения команд от используемых ими данных, и это может быть жёстко сконфигурировано.

3. Состояние регистра CCR после сброса определяется конфигурацией процессора.

4. Регистр DFSR устанавливается в 0 только сбросом по включению питания.

Помимо регистров, входящих в состав SCB, важную роль в управлении вычислительной системой играют некоторые другие регистры, не вошедшие в отдельную категорию, а также регистры контроллера прерываний, таймера и устройства защиты памяти. В процессорах, имеющих FPU, к ним добавляются регистры управления FPU. Последние документация ARM относит к регистрам SCB, хотя они, как и другие перечисленные здесь регистры различных технических средств, занимают адреса, относящиеся к другим областям SCS.

Описание регистров SCB[]

Основной регистр идентификации процессора CPUID[]

Адрес: E000ED00.

Доступ: только чтение. В версии ARMv8.1-M этот регистр доступен для непривилегированных запросов отладчика, только если установлен любой из битов DAUTHCTRL_S.UIDAPEN или DAUTHCTRL_NS.UIDAPEN.

Наличие: всегда.

Этот регистр служит одним из средств идентификации процессора, на котором выполняется программа. Назначение его полей:

| Разряды | Доступ | Обозначение | Функция |

|---|---|---|---|

| Код разработчика, выданный компанией ARM. Сама ARM для своих разработок использует код 41. | |||

| Номер варианта архитектуры, определяемый реализацией. | |||

| Код версии архитектуры. Содержит значение 1100 для ARMv6-M и 1111 для ARMv7-M. Для ARMv8-M, судя по всему, используются эти же значения в зависимости от того, имеется или нет базовое расширение, т.е. преемницей какой из предыдущих версий архитектуры является данная реализация. | |||

| Номер компонента, определяемый реализацией. | |||

| Номер ревизии, определяемый реализацией. |

Известные значения этого регистра (r и p означают ревизию ядра и её патч):

- 41rCC20p — Cortex-M0

- 41rCC60p — Cortex-M0+

- 41rCC21p — Cortex-M1

- 41rFС23p — Cortex-M3 (для Cortex-M3 r2p1 в его TRM указано значение 0x410FC241 — что, очевидно, является ошибкой, так как соответствует ядру Cortex-M4 r0p1)

- 41rFС24p — Cortex-M4

- 41rFС27p — Cortex-M7

- 41rCD20p — Cortex-M23

- 41rFD21p — Cortex-M33

- 41rFD22p — Cortex-M55

Регистр состояния и управления прерываниями ICSR[]

Адрес: E000ED04.

Доступ: чтение/запись. При наличии расширения безопасности регистр имеет отдельные версии для каждого из режимов.

Наличие: всегда.

| Разряды | Доступ | Обозначение | Функция |

|---|---|---|---|

|

Чтение:

Запись:

Если биты NMIPENDSET и PENDNMICLR одновременно установлены, результат непредсказуем. Поддержка режимов безопасности. Этот бит не имеет отдельных версий для режимов безопасности. Если бит AIRCR.BFHFNMINS сброшен, считывание этого бита в небезопасном режиме возвращает нуль, а запись игнорируется. Примечание. Ядро Cortex-M1 сбрасывает этот запрос при записи единицы в бит AIRCR.VECTCLRACTIVE, хотя официально об этом в документации не говорится. | |||

|

Запись:

Если биты NMIPENDSET и PENDNMICLR одновременно установлены, результат непредсказуем. Поддержка режимов безопасности. Этот бит не имеет отдельных версий для режимов безопасности. Если бит AIRCR.BFHFNMINS сброшен, запись в него в небезопасном режиме игнорируется. Этот бит появился в версии ARMv8-M. | |||

| Зарезервирован. | |||

|

Чтение:

Запись:

Результат одновременной записи единиц в биты PENDSVSET и PENDSVCLR непредсказуем. Поддержка режимов безопасности. Этот бит имеет отдельные версии для режимов безопасности. Этот бит отсутствует, если прерывание PendSV не поддерживается. Примечание. В ядре Cortex-M1 даже при наличии системных расширений этот бит доступен только для записи (при считывании возвращается нуль), что противоречит руководству по архитектуре ARMv6-M. | |||

|

Запись:

Результат одновременной записи единиц в биты PENDSVSET и PENDSVCLR непредсказуем. Поддержка режимов безопасности. Этот бит имеет отдельные версии для режимов безопасности. Этот бит отсутствует, если прерывание PendSV не поддерживается. | |||

|

Чтение:

Запись:

Результат одновременной записи единиц в биты PENDSTSET и PENDSTCLR непредсказуем. Поддержка режимов безопасности. Этот бит имеет отдельные версии для режимов безопасности, если для них предусмотрены отдельные таймеры. Если имеется один общий таймер, то при сброшенном бите ICSR.STTNS запись единицы в бит PENDSTSET игнорируется, а при считывании возвращается нуль. Этот бит отсутствует, если SysTick не реализован. Примечание. В ядре Cortex-M1 даже при наличии SysTick этот бит доступен только для записи (при считывании всегда возвращается нуль), что противоречит руководству по архитектуре ARMv6-M. | |||

|

Запись:

Результат одновременной записи единиц в биты PENDSTSET и PENDSTCLR непредсказуем. Поддержка режимов безопасности. Этот бит имеет отдельные версии для режимов безопасности, если для них предусмотрены отдельные таймеры. Если имеется один общий таймер, то при сброшенном бите ICSR.STTNS запись единицы в бит PENDSTCLR игнорируется. Этот бит отсутствует, если SysTick не реализован. | |||

|

Показывает доступность SysTick небезопасному коду:

Поддержка режимов безопасности. Этот бит имеется только при наличии расширения безопасности и только в случае, если реализован лишь один таймер; в этом случае он доступен лишь из безопасного режима. При наличии двух таймеров или при их отсутствии он всегда считывается как нуль, а запись в него игнорируется. Этот бит появился в ARMv8-M с расширением безопасности и одним SysTick. | |||

|

Показывает, будет ли при выходе из отладочного останова начата обработка ожидающего прерывания:

Состояние этого бита не определено, если процессор не находится в отладочном останове. Поддержка режимов безопасности. Этот бит не имеет отдельных версий для режимов безопасности. В версиях ARMv8-M без основного расширения и ARMv6-M этот бит имеется лишь при поддержке отладки. | |||

|

Показывает, имеется ли ожидающее обработки внешнее прерывание:

Этот бит формируется без учёта состояния бита DHCSR.C_MASKINTS, т. е. показывает лишь наличие запросов прерываний, но не возможность вызова их обработчиков. Поддержка режимов безопасности. Этот бит не имеет отдельных версий для режимов безопасности. В версиях ARMv8-M без основного расширения и ARMv6-M этот бит имеется лишь при поддержке отладки. | |||

| Зарезервирован. | |||

|

Номер самого приоритетного из ожидающих разрешённых запросов прерываний. Учитывается запрет отдельных запросов их масками или битом DHCSR.C_MASKINTS, но не учитывается общий запрет прерываний битом PRIMASK.PM. Если таковых нет, содержит нуль. Поддержка режимов безопасности. Это поле не имеет отдельных версий для режимов безопасности. Однако, начиная с ARMv8.1-M, оно содержит 1, если из безопасного режима считывается регистр небезопасного режима, а самым приоритетным является запрос прерывания для безопасного режима. Примечание. В ядре Cortex-M1 это поле присутствует лишь в случае, если поддерживаются системные расширения, хотя по документации на архитектуру ARMv6-M оно является обязательным. | |||

|

При опросе из режима обработчика показывает, имеется ли ещё какое-либо активное прерывание, помимо обрабатываемого в данный момент:

В режиме потока значение этого бита не определено. Поддержка режимов безопасности. Этот бит не имеет отдельных версий для режимов безопасности. В версиях ARMv8-M без основного расширения и ARMv6-M этот бит зарезервирован. | |||

| Зарезервированы. | |||

|

Номер прерывания, чей обработчик выполняется в данный момент; 0 для режима потока. Значение этого поля совпадает с битами 8:0 регистра IPSR. Поддержка режимов безопасности. Этот бит не имеет отдельных версий для режимов безопасности. В версиях ARMv8-M без основного расширения и ARMv6-M это поле присутствует лишь при поддержке отладки. |

Регистр адреса таблицы векторов прерываний VTOR[]

Адрес: E000ED08.

Доступ: только чтение или чтение/запись в зависимости от реализации. Начальное значение и количество реализованных разрядов также определяются реализацией. При наличии расширения безопасности регистр имеет отдельные версии для каждого из режимов.

Наличие: всегда

| Разряды | Доступ | Обозначение | Функция |

|---|---|---|---|

| Старшие разряды адреса таблицы векторов. | |||

| Зарезервированы. |

В некоторых реализациях один или два старших бита поля TBLOFF могут быть жёстко заведены на 0, что ограничивает выбор положения таблицы векторов в памяти. Чтобы проверить возможности размещения таблицы векторов, программа может записать в регистр VTOR все единицы, а затем считать из него реально записанное значение.

Примечание. В ранних версиях документации писалось, что поле TBLOFF содержит смещение таблицы векторов; отсюда произошли аббревиатуры VTOR и TBLOFF. Позднее вместо некорректного для данного случая термина «смещение» стали применять правильный «адрес», однако обозначения регистра и поля оставили без изменений.

Регистр управления сбросами и прерываниями AIRCR[]

Адрес: E000ED0C.

Доступ: чтение/запись. При наличии расширения безопасности регистр имеет отдельные версии для каждого из режимов.

Наличие: всегда.

| Разряды | Доступ | Обозначение | Функция |

|---|---|---|---|

VECTKEYSTAT |

Чтение: в ARMv6-M значение не определено, в остальных версиях – константа FA05. Запись: в ARMv6-M, если при записи в регистр значение этого поля не равно 05FA, последствия будут непредсказуемы; в остальных версиях такая запись будет проигнорирована. Поддержка режимов безопасности. Это поле не имеет отдельных версий для режимов безопасности. | ||

|

Указывает на принятый в данной реализации порядок следования байтов данных в памяти (за исключением SCS):

Поддержка режимов безопасности. Этот бит не имеет отдельных версий для режимов безопасности. | |||

|

Управление приоритетами небезопасных прерываний:

Поддержка режимов безопасности. Этот бит не имеет отдельных версий для режимов безопасности и реализован лишь при наличии расширения безопасности. Запись этого бита из небезопасного кода игнорируется, считывание возвращает нуль. Возможность записи в него безопасным кодом определяется реализацией. Этот бит появился в ARMv8-M. | |||

|

Управление режимом обработки прерываний NMI, HardFault и BusFault:

Если одновременно установлены биты BFHFNMINS и PRIS, последствия будут непредсказуемы. Поддержка режимов безопасности. Этот бит реализован лишь в процессорах с расширением безопасности. Возможность его записи безопасным кодом определяется реализацией; небезопасный код может только считывать его значение. В ARMv8-M, если расширение безопасности отсутствует, этот бит, как утверждает документация, считывается как единица, однако она же утверждает, что тёплым сбросом он обнуляется. Вероятно, это ошибка, и при отсутствии расширения безопасности он всегда равен нулю (что соответствует более ранним версиям архитектуры). Этот бит появился в ARMv8-M. | |||

| Зарезервированы. | |||

|

Это поле управляет группированием приоритетов прерываний. Поддержка режимов безопасности. При наличии расширения безопасности каждый режим имеет свою версию этого поля. В версиях ARMv8-M без основного расширения и ARMv6-M группирование не поддерживается, и эти разряды зарезервированы. | |||

| Зарезервированы. | |||

|

Управление неявным барьером синхронизации ошибок (ESB):

ESB может вставляться при входе и выходе из прерывания и при отложенном сохранении контекста FPU. Кроме того, когда он разрешён, неточные прерывания BusFault будут вызывать повышение приоритета подобно точным отказам, но, поскольку реальное место возникновения такого отказа неизвестно, всё равно в качестве причины прерывания будет указываться неточный отказ. Поддержка режимов безопасности. У этого бита нет отдельных версий для режимов безопасности, однако при наличии расширения безопасности, если бит AIRCR.BFHFNMINS сброшен, небезопасный код будет считывать его как нуль, а запись будет игнорироваться. Этот бит появился в ARMv8-M с поддержкой RAS; возможность его программного изменения и состояние после сброса определяется реализацией. Насчёт состояния этого бита документация противоречива: с одной стороны, прямо говорится, что тёплый сброс его обнуляет, с другой стороны, столь же прямо утверждается, что процессор может быть жёстко сконфигурирован на применение или неприменение ESB, что будет отражаться данным битом при его считывании. | |||

|

Управление независимым от данных временем выполнения команд (DIT):

Поддержка режимов безопасности. Каждый режим безопасности имеет свой вариант этого бита. Этот бит появился в ARMv8-M с поддержкой DIT. Возможность его программного изменения, а также его состояние после сброса определяется реализацией (в части сброса документация противоречит сама себе, утверждая, что он сбрасывается в нуль, и одновременно утверждая, что он показывает, зависит время выполнения команд от данных или нет). | |||

|

Разрешение сброса небезопасным кодом:

Поддержка режимов безопасности. Этот бит не имеет версий для разных режимов безопасности и недоступен для небезопасного кода. Этот бит появился в ARMv8-M. | |||

|

Запрос выполнения тёплого сброса:

Поддержка режимов безопасности. Этот бит не имеет версий для разных режимов безопасности. В процессорах с расширением безопасности небезопасная запись в него игнорируется, если установлен бит AIRCR.SYSRESETREQS. Сброс может быть произведён в любой момент после установки данного бита, но не обязательно немедленно после такой установки. Документация на ARMv6-M указывает данный бит как доступный только для записи, на ARMv8-M — как на доступный для чтения и записи; для ARMv7-M информация не приводится. | |||

|

Сброс состояния активности прерываний:

Этот бит сбрасывается автоматически. Запись единицы, если процессор не находится в отладочном останове, в ARMv6-M и ARMv7-M приведёт к непредсказуемым результатам; в ARMv8-M она будет проигнорирована. Поддержка режимов безопасности. Этот бит не имеет версий для разных режимов безопасности. В процессорах с расширением безопасности запись в него единицы всегда сбрасывает IPSR; признаки активности небезопасных прерываний сбрасываются только в случае, если сброшен бит DHCSR.S_NSUIDE; признаки активности безопасных прерываний сбрасываются только в случае, если сброшен бит DHCSR.S_SUIDE и установлен бит DHCSR.S_SDE. Примечание. В ядре Cortex-M1 запись 1 в этот разряд приводит к сбросу не только активных, но и ожидающих запросов прерываний NMI и HardFault, хотя документация на архитектуру не упоминает о такой возможности. Кроме того, его установка вызывает сброс состояния блокировки процессора. | |||

|

Запрос выполнения локального сброса:

Этот бит сбрасывается автоматически. Если при записи 1 процессор не находится в отладочном останове, а также если этот бит устанавливается совместно с битом AIRCR.SYSRESETREQ, результаты будут непредсказуемы. Этот бит имеется лишь в версии ARMv7-M. |

Регистр управления системой SCR[]

Адрес: E000ED10.

Доступ: чтение/запись. При наличии расширения безопасности регистр имеет отдельные версии для каждого из режимов.

Наличие: всегда в ARMv7-M и ARMv8-M, только при поддержке управления питанием в командах WFI и WFE в ARMv6-M.

| Разряды | Доступ | Обозначение | Функция |

|---|---|---|---|

| Зарезервированы. | |||

Определяет, является ли появление ожидающего запроса прерывания сигналом пробуждения для команды WFE:

Поддержка режимов безопасности. Каждый режим безопасности имеет свою версию этого бита, управляющую выдачей сигнала пробуждения при поступлении запросов прерываний только этого режима. | |||

Управление использованием бита SLEEPDEEP:

Поддержка режимов безопасности. Этот бит не имеет отдельных версий для разных режимов. В небезопасном режиме запись в него игнорируется, а считывание возвращает нуль. Этот бит появился в версии ARMv8-M. Если глубокий сон не поддерживается, этот бит всегда равен нулю. | |||

|

Определяет, в насколько глубокий сон может погружаться процессор при переходе в ожидание:

Поддержка режимов безопасности. Этот бит не имеет отдельных версий для разных режимов. Возможность доступа к нему в небезопасном режиме определяется битом SCR.SLEEPDEEPS. Поддержка различных видов сна и их конкретный смысл определяются реализацией. Если состояние глубокого сна не поддерживается, запись в этот бит игнорируется, а при считывании всегда возвращается нуль. | |||

|

Определяет, необходимо ли переходить в сон по завершении последнего активного обработчика прерывания:

Поддержка режимов безопасности. Этот бит имеет отдельные версии для каждого режима безопасности и управляет переходом в сон при завершении всех обработчиков соответствующего режима. | |||

| Зарезервирован. |

Регистр управления и конфигурации CCR[]

Адрес: E000ED14.

Доступ: только чтение в ARMv6-M, чтение/запись в остальных версиях. При наличии расширения безопасности регистр имеет отдельные версии для каждого из режимов.

Наличие: всегда.

| Разряды | Доступ | Обозначение | Функция |

|---|---|---|---|

| Зарезервированы | |||

|

Проверка сигнатуры целостности и запрет повторного входа в поток в командах SG:

Поддержка режимов безопасности. Этот бит реализован только при наличии расширения безопасности и не имеет отдельных версий для разных режимов. Небезопасная запись в него игнорируется, считывание возвращает нуль. Этот бит появился в версии ARMv8.1-M. | |||

|

Разрешение работы кэша циклов и переходов:

Поддержка режимов безопасности. Этот бит имеет отдельные версии для каждого режима, управляющие кэшем для этого режима. Этот бит появился в версии ARMv8.1-M. Он равен нулю в более ранних версиях, а также при отсутствии кэша циклов и переходов. | |||

|

Управляет работой предсказателя переходов:

Поддержка режимов безопасности. Этот бит имеет отдельные версии для каждого режима, управляющие предсказателем для этого режима. Если предсказатель переходов отсутствует, этот бит всегда будет равен нулю. Если он присутствует и не может быть выключен, этот бит всегда будет равен единице. В версиях ARMv8-M без основного расширения и ARMv-6 всегда равен нулю. | |||

|

Управляет работой кэша команд:

Поддержка режимов безопасности. Этот бит имеет отдельные версии для каждого режима, управляющие кэшем для этого режима. Перед включением необходимо выполнить инвалидацию кэша, после включения – барьер синхронизации команд. В версиях ARMv8-M без основного расширения и ARMv-6, а также при отсутствии кэша в других версиях этот бит равен нулю. | |||

|

Управляет работой кэша данных и/или общего кэша команд и данных:

Поддержка режимов безопасности. Этот бит имеет отдельные версии для каждого режима, управляющие кэшем для этого режима. Перед включением необходимо выполнить инвалидацию кэша, после включения – барьер синхронизации команд. Кроме того, при выключении надо выполнить очистку кэша, чтобы все изменённые данные были гарантированно записаны в память. В версиях ARMv8-M без основного расширения и ARMv-6, а также при отсутствии кэша в других версиях этот бит равен нулю. | |||

| Зарезервированы. | |||

|

Игнорирование отказов из-за выхода за пределы стека при работе на уровне привилегий меньше нуля (NMI или HardFault):

Поддержка режимов безопасности. Этот бит имеет отдельные версии для каждого режима, управляющие контролем стека для этого режима. Этот бит присутствует только в архитектуре ARMv8-M с основным расширением. | |||

|

Определяет, необходимо ли при входе в обработчик прерывания принудительно выравнивать стек на границу двойного слова:

Если процессор имеет и использует FPU, стек всегда выравнивается на границу двойного слова независимо от состояния этого разряда. Конкретная реализация версии ARMv7-M может сделать этот бит неизменяемым; ARM рекомендует в таких случаях использовать принудительное выравнивание на границу двойного слова. Версии ARMv6-M и ARMv8-M всегда обеспечивают принудительное выравнивание, а этот бит доступен только для чтения, возвращая единицу. | |||

|

Определяет, необходимо ли вырабатывать прерывание при точном отказе во время доступа к данным в обработчике NMI или HardFault:

Поддержка режимов безопасности. Этот бит не имеет отдельных версий для режимов безопасности. Если расширение безопасности реализован, он доступен из небезопасного режима только при установленном бите AIRCR.BFHFNMINS. В версиях ARMv8-M без основного расширения и ARMv6-M этот бит зарезервирован. | |||

| Зарезервированы. | |||

|

Управляет возникновением отказа при делении на 0:

Поддержка режимов безопасности. Этот бит имеет отдельные версии для каждого режима безопасности. В версиях ARMv8-M без основного расширения и ARMv6-M этот бит зарезервирован. | |||

|

Управляет возникновением отказа при выполнении невыровненного доступа:

Поддержка режимов безопасности. Этот бит имеет отдельные версии для каждого режима безопасности. В версиях ARMv8-M без основного расширения и ARMv6-M этот бит зарезервирован и равен единице. | |||

| Зарезервирован. | |||

|

Управляет доступом непривилегированного кода к регистру STIR:

Поддержка режимов безопасности. Этот бит имеет отдельные версии для каждого режима безопасности. В версиях ARMv8-M без основного расширения и ARMv6-M этот бит зарезервирован. | |||

|

Управляет возможностью входа процессора в режим потока при приоритете выполнения, отличном от базового:

В версиях ARMv6-M и ARMv8-M этот бит зарезервирован. |

Регистры приоритетов системных обработчиков SHPR1, SHPR2, SHPR3[]

Адрес: E000ED18, E000ED1C, E000ED20.

Доступ: только словами в ARMv8-M без основного расширения и в ARMv6-M, словами, полусловами и байтами в ARMv8-M с основным расширением и в ARMv7-M. При наличии расширения безопасности эти регистры имеют отдельные версии для каждого из режимов. Начиная с ARMv8.1-M, может ли отладчик осуществлять запись в эти регистры, если процессор не остановлен, зависит от реализации.

Наличие: SHPR1 отсутствует в ARMv8-M без основного расширения и в ARMv6-M, остальные регистры присутствуют всегда.

Все три регистра имеют одинаковую структуру и разделены на четыре 8-разрядных поля, каждое из которых задаёт приоритет соответствующего обработчика прерывания. Регистр SHPR1 определяет приоритеты прерываний с номерами 4–7, SHPR2 — с номерами 8–11, SHPR3 — с номерами 12–15. Число реально используемых разрядов в каждом поле может быть меньше 8 и определяется реализацией (реализованные разряды всегда являются старшими в каждом из байтов).

Регистр состояния и управления системными обработчиками SHCSR[]

Адрес: E000ED24.

Доступ: чтение/запись. При наличии расширения безопасности этот регистр имеет отдельные версии для каждого из режимов. В ARMv6-M доступность этого регистра со стороны процессора определяется реализацией. Начиная с ARMv8.1-M, возможность записи в этот регистр отладчиком, если процессор не остановлен, определяется реализацией.

Наличие: только при поддержке отладки в ARMv6-M, всегда в остальных версиях.

| Разряды | Доступ | Обозначение | Функция |

|---|---|---|---|

| Зарезервированы. | |||

|

Наличие запроса прерывания HardFault:

Поддержка режимов безопасности. Этот бит имеет отдельные версии для каждого режима. Если бит AIRCR.BFHFNMINS сброшен, небезопасный код не имеет доступа к этому биту. Этот бит появился в ARMv8-M. | |||

|

Наличие запроса прерывания SecureFault:

Поддержка режимов безопасности. Этот бит имеется только при наличии расширения безопасности и не имеет отдельных версий для разных режимов. Он доступен только безопасному коду. Этот бит появился в ARMv8-M с основным расширением. | |||

|

Разрешение прерывания SecureFault:

Поддержка режимов безопасности. Этот бит имеется только при наличии расширения безопасности и не имеет отдельных версий для разных режимов. Он доступен только безопасному коду. Этот бит появился в ARMv8-M с основным расширением. | |||

|

Разрешение прерывания UsageFault:

Поддержка режимов безопасности. Этот бит имеет отдельные версии для каждого режима. Этот бит отсутствует в ARMv8-M без основного расширения и в ARMv6-M. | |||

|

Разрешение прерывания BusFault:

Поддержка режимов безопасности. Этот бит имеет отдельные версии для каждого режима. Этот бит отсутствует в ARMv8-M без основного расширения и в ARMv6-M. | |||

|

Разрешение прерывания MemManage:

Поддержка режимов безопасности. Этот бит имеет отдельные версии для каждого режима. Этот бит отсутствует в ARMv8-M без основного расширения и в ARMv6-M. | |||

|

Наличие запроса прерывания SVCall:

Поддержка режимов безопасности. Этот бит имеет отдельные версии для каждого режима. Этот бит отсутствует в ARMv6-M без системного расширения. | |||

|

Наличие запроса прерывания BusFault:

Поддержка режимов безопасности. Этот бит имеет отдельные версии для каждого режима. Этот бит отсутствует в ARMv8-M без основного расширения и в ARMv6-M. | |||

|

Наличие запроса прерывания MemManage:

Поддержка режимов безопасности. Этот бит имеет отдельные версии для каждого режима. Этот бит отсутствует в ARMv8-M без основного расширения и в ARMv6-M. | |||

|

Наличие запроса прерывания UsageFault:

Поддержка режимов безопасности. Этот бит имеет отдельные версии для каждого режима. Этот бит отсутствует в ARMv8-M без основного расширения и в ARMv6-M. | |||

|

Признак активности прерывания SysTick:

Поддержка режимов безопасности. Если имеется расширение безопасности и для каждого из режимов реализован свой таймер, этот бит также имеет отдельную версию для каждого из режимов. Если же таймер общий для обоих режимов, то при сброшенном бите ICSR.STTNS данный бит используется только в безопасном режиме, а при установленном — в небезопасном режиме. Этот бит отсутствует в ARMv6-M независимо от наличия таймера. | |||

|

Активность прерывания PendSV:

Поддержка режимов безопасности. Этот бит имеет отдельные версии для каждого режима. Этот бит отсутствует в ARMv6-M независимо от наличия системного расширения. | |||

| Зарезервирован | |||

|

Активность прерывания DebugMonitor:

Поддержка режимов безопасности. Этот бит не имеет отдельных версий для каждого режима. Если бит DEMCR.SDME установлен, доступ к биту MONITORACT у небезопасного кода отсутствует. Этот бит отсутствует в ARMv8-M без основного расширения и в ARMv6-M. | |||

|

Активность прерывания SVCall:

Поддержка режимов безопасности. Этот бит имеет отдельные версии для каждого режима. Этот бит отсутствует в ARMv6-M независимо от наличия системного расширения. | |||

| Зарезервирован. | |||

|

Активность прерывания NMI:

Поддержка режимов безопасности. Этот бит не имеет отдельных версий для каждого режима. Если AIRCR.BFHFNMINS сброшен, небезопасный код не имеет к нему доступа. Запись в этот бит игнорируется, если либо 1) записывается единица, бит AIRCR.BFHFNMINS сброшен, доступ выполняется из небезопасного состояния и не к SHCSR_NS, либо 2) запись выполняется отладчиком и бит DHCSR.S_SDE сброшен. Этот бит может быть сброшен только доступом из безопасного режима к SHCSR_NS. Формулировка в документации прямолинейна, но невнятна: 1) с одной стороны, отладчик может изменять этот бит, если DHCSR.S_SDE установлен, а с другой — возможность сброса прямо отнесена только к программному доступу из безопасного кода к SHCSR_NS; 2) непонятно, можно ли программно установить этот бит: четыре условия, когда запись в него игнорируются, перечислены без союзов, что предполагает союз «и», но тогда формально он может обнуляться любым кодом без дополнительных условий, что не так, поэтому, вероятно, он может устанавливаться безопасным кодом при доступе к SHCSR_NS, если сама обработка NMI выполняется небезопасным кодом (AIRCR.BFHFNMINS установлен). Этот бит появился в ARMv8-M. | |||

|

Активность прерывания SecureFault:

Поддержка режимов безопасности. Этот бит не имеет отдельных версий для каждого режима; небезопасному коду он недоступен. Этот бит появился в ARMv8-M. | |||

|

Активность прерывания UsageFault:

Поддержка режимов безопасности. Этот бит имеет отдельные версии для каждого режима. Этот бит отсутствует в ARMv8-M без основного расширения и в ARMv6-M. | |||

|

Активность прерывания HardFault:

Поддержка режимов безопасности. Этот бит имеет отдельные версии для каждого режима. Программная установка этого бита невозможна; программный сброс (запись нуля) возможен только для небезопасной версии регистра (через SHCSR_NS) и только отладчиком при установленном бите DHCSR.S_SDE либо безопасным кодом. Этот бит появился в ARMv8-M. | |||

|

Активность прерывания BusFault:

Поддержка режимов безопасности. Этот бит не имеет отдельных версий для каждого режима. Если бит AIRCR.BFHFNMINS сброшен, небезопасный код не имеет доступа к этому биту. Этот бит отсутствует в ARMv8-M без основного расширения и в ARMv6-M. | |||

|

Активность прерывания MemManage:

Поддержка режимов безопасности. Этот бит имеет отдельные версии для каждого режима. Этот бит отсутствует в ARMv8-M без основного расширения и в ARMv6-M. |

Разряды, указывающие нахождение прерывания в состоянии ожидания, устанавливаются аппаратно при появлении соответствующего запроса (или при его программной установке) и сбрасываются при вызове обработчика (или при программном сбросе запроса). Разряды, указывающие нахождение прерывания в активном состоянии, устанавливаются при вызове обработчика и остаются установленными до тех пор, пока не произойдёт возврат из соответствующего обработчика (или не будут сброшены признаки всех активных прерываний). Они остаются установленными, если обработчик оказывается прерванным обработчиком более приоритетного запроса.

Программа может не только считывать, но и записывать почти любые разряды этого регистра (об ограничениях сказано в их описании), изменяя этим путём текущее состояние обработки прерываний. Это может привести к нарушению принципов обработки прерываний, предусмотренных архитектурой. Возможность программной записи предусмотрена, главным образом, в отладочных целях.

Примечание. В ядре Cortex-M1 запись в этот регистр возможна только со стороны отладчика, запись со стороны процессора игнорируется, хотя это и противоречит описанию архитектуры ARMv6-M.

Регистр состояния отказов с настраиваемыми приоритетами CFSR[]

Адрес: E000ED28.

Доступ: чтение/запись словами, полусловами и байтами; запись единицы очищает соответствующий бит. При наличии расширения безопасности этот регистр имеет отдельные версии для каждого из режимов. Начиная с ARMv8.1-M, возможность записи в этот регистр отладчиком, если процессор не остановлен, определяется реализацией.

Наличие: только ARMv8-M с основным расширением и ARMv7-M.

| Разряды | Доступ | Обозначение | Функция |

|---|---|---|---|

| Индикаторы активных причин возникновения прерывания UsageFault | |||

| Индикаторы активных причин возникновения прерывания BusFault | |||

| Индикаторы активных причин возникновения прерывания MemManage |

Технически регистр CFSR состоит из трёх независимых регистров: MMFSR, BFSR и UFSR, описанных ниже.

Регистр состояния прерывания MemManage MMFSR[]

Адрес: E000ED28.

Доступ: чтение/запись отдельным байтом или словом в составе CFSR; запись единицы очищает соответствующий бит. При наличии расширения безопасности этот регистр имеет отдельные версии для каждого из режимов. Начиная с ARMv8.1-M, возможность записи в этот регистр отладчиком, если процессор не остановлен, определяется реализацией.

Наличие: только ARMv8-M с основным расширением и ARMv7-M.

| Разряды | Доступ | Обозначение | Функция |

|---|---|---|---|

Поддержка режимов безопасности. Этот бит имеет отдельные экземпляры для каждого из режимов. | |||

| Зарезервирован. | |||

|

Установлен, если прерывание MemManage возникло при отложенном сохранении состояния FPU. Поддержка режимов безопасности. Этот бит имеет отдельные экземпляры для каждого из режимов. | |||

|

Установлен, если прерывание MemManage возникло при входе в обработчик какого-либо прерывания. Поддержка режимов безопасности. Этот бит имеет отдельные экземпляры для каждого из режимов. | |||

|

Установлен, если прерывание MemManage возникло при выходе из обработчика какого-либо прерывания. Поддержка режимов безопасности. Этот бит имеет отдельные экземпляры для каждого из режимов. | |||

| Зарезервирован. | |||

|

Установлен, если обнаружено нарушение прав доступа к данным; адрес этих данных находится в MMAR. Поддержка режимов безопасности. Этот бит имеет отдельные экземпляры для каждого из режимов. | |||

|

Установлен, если прерывание MemManage возникло при попытке выборки команды для фактического выполнения. Поддержка режимов безопасности. Этот бит имеет отдельные экземпляры для каждого из режимов. |

Регистр состояния прерывания BusFault BFSR[]

Адрес: E000ED29.

Доступ: чтение/запись отдельным байтом или словом в составе CFSR; запись единицы очищает соответствующий бит. При наличии расширения безопасности этот регистр не имеет отдельных версий для каждого из режимов. Начиная с ARMv8.1-M, возможность записи в этот регистр отладчиком, если процессор не остановлен, определяется реализацией.

Наличие: только ARMv8-M с основным расширением и ARMv7-M.

| Разряды | Доступ | Обозначение | Функция |

|---|---|---|---|

Поддержка режимов безопасности. Если AIRCR.BFHFNMINS сброшен, этот бит в небезопасном состоянии недоступен. | |||

| Зарезервирован. | |||

|

Равен единице, если прерывание BusFault возникло при отложенном сохранении состояния FPU. Поддержка режимов безопасности. Если AIRCR.BFHFNMINS сброшен, этот бит в небезопасном состоянии недоступен. | |||

|

Равен единице, если прерывание BusFault возникло при попытке входа в обработчик какого-либо прерывания. Поддержка режимов безопасности. Если AIRCR.BFHFNMINS сброшен, этот бит в небезопасном состоянии недоступен. | |||

|

Равен единице, если прерывание BusFault возникло при попытке выхода из обработчика какого-либо прерывания. Поддержка режимов безопасности. Если AIRCR.BFHFNMINS сброшен, этот бит в небезопасном состоянии недоступен. | |||

|

Равен единице, если при обращении к данным возник неточный отказ. Поддержка режимов безопасности. Если AIRCR.BFHFNMINS сброшен, этот бит в небезопасном состоянии недоступен. | |||

|

Равен единице, если при обращении к данным возник точный отказ; его адрес занесён в BFAR. Поддержка режимов безопасности. Если AIRCR.BFHFNMINS сброшен, этот бит в небезопасном состоянии недоступен. | |||

|

Равен единице, если прерывание BusFault возникло при попытке выборки команды для фактического выполнения. Поддержка режимов безопасности. Если AIRCR.BFHFNMINS сброшен, этот бит в небезопасном состоянии недоступен. |

Регистр состояния прерывания UsageFault UFSR[]

Адрес: E000ED2A.

Доступ: чтение/запись отдельными байтами, полусловом или словом в составе CFSR; запись единицы очищает соответствующий бит. При наличии расширения безопасности этот регистр имеет отдельные версии для каждого из режимов. Начиная с ARMv8.1-M, возможность записи в этот регистр отладчиком, если процессор не остановлен, определяется реализацией.

Наличие: только ARMv8-M с основным расширением и ARMv7-M.

| Разряды | Доступ | Обозначение | Функция |

|---|---|---|---|

| Зарезервированы. | |||

|

Установлен, если прерывание UsageFault вызвано попыткой деления на 0. Поддержка режимов безопасности. Этот бит имеет отдельные версии для каждого режима. | |||

|

Установлен, если прерывание UsageFault вызвано попыткой невыровненного доступа. Поддержка режимов безопасности. Этот бит имеет отдельные версии для каждого режима. | |||

| Зарезервированы. | |||

|

Установлен, если прерывание UsageFault вызвано переполнением стека. Поддержка режимов безопасности. Этот бит имеет отдельные версии для каждого режима. Этот бит появился в ARMv8-M. | |||

|

Установлен, если прерывание UsageFault вызвано обращением к сопроцессору, доступ к которому запрещён. Поддержка режимов безопасности. Этот бит имеет отдельные версии для каждого режима. | |||

|

Установлен, если прерывание UsageFault вызвано выполнением возврата из прерывания с неверным значением EXC_RETURN. Поддержка режимов безопасности. Этот бит имеет отдельные версии для каждого режима. | |||

|

Установлен, если прерывание UsageFault вызвано попыткой выполнения команды при неверном значении бита T или поля IT EPSR. Поддержка режимов безопасности. Этот бит имеет отдельные версии для каждого режима. | |||

|

Установлен, если прерывание UsageFault вызвано попыткой выполнения отсутствующей команды либо привилегированной команды в непривилегированном режиме. Поддержка режимов безопасности. Этот бит имеет отдельные версии для каждого режима. |

Регистр состояния прерывания HardFault HFSR[]

Адрес: E000ED2C

Доступ: чтение/запись; запись единицы очищает соответствующий бит. Отдельных версий для каждого режима безопасности этот регистр не имеет. Начиная с ARMv8.1-M, возможность записи в этот регистр отладчиком, если процессор не остановлен, определяется реализацией.

Наличие: только ARMv8-M с основным расширением и ARMv7-M.

| Разряды | Доступ | Обозначение | Функция |

|---|---|---|---|

|

Установлен, если прерывание HardFault произошло из-за того, что возникло отладочное событие, при этом отладочный останов запрещён, а прерывание DebugMon не может быть вызвано. | |||

|

Установлен, если прерывание HardFault произошло из-за повышения приоритета синхронного прерывания до HardFault. | |||

| Зарезервированы. | |||

|

Установлен, если прерывание HardFault произошло из-за ошибки при попытке прочитать таблицу векторов прерываний. | |||

| Зарезервирован. |

Регистр адреса отказа памяти MMFAR[]

Адрес: E000ED34.

Доступ: чтение/запись. При наличии расширения безопасности имеет отдельные версии для разных режимов безопасности. Начиная с ARMv8.1-M, возможность записи в этот регистр отладчиком, если процессор не остановлен, определяется реализацией.

Наличие: только ARMv8-M с основным расширением и ARMv7-M.

| Разряды | Доступ | Обозначение | Функция |

|---|---|---|---|

|

Адрес, при попытке обращения по которому возникло прерывание MemManage, вызванное обнаруженным MPU нарушением защиты памяти. Если выполнялся невыровненный доступ, в регистре MMFAR будет находиться адрес, реально вызвавший нарушение защиты; он может не совпадать с адресом, использованным в команде. Содержимое этого регистра действительно лишь при установленном бите MMFSR.MMARVALID. Регистр MMFAR может технически совпадать с регистром BFAR, поскольку прерывания MemManage и BusFault не могут произойти одновременно. В такой ситуации, если после прерывания MemManage происходит прерывание BusFault, содержимое регистра MMFAR изменяется и уже не отражает адрес, вызвавший прерывание MemManage. Произойдёт ли при этом сброс бита MMFSR.MMARVALID, документация не сообщает. Поддержка режимов безопасности. Это поле имеет отдельные версии для каждого из режимов. Состояние после сброса не определено. |

Регистр адреса отказа шины BFAR[]

Адрес: E000ED38.

Доступ: чтение/запись. Отдельных версий для разных режимов безопасности не имеет. Начиная с ARMv8.1-M, возможность записи в этот регистр отладчиком, если процессор не остановлен, определяется реализацией.

Наличие: только ARMv8-M с основным расширением и ARMv7-M.

| Разряды | Доступ | Обозначение | Функция |

|---|---|---|---|

|

Адрес данных, при обращении по которому возник точный отказ BusFault. Если отказ произошёл при невыровненном доступе, в BFAR будет находиться адрес, использованный командой, вызвавшей отказ; он не обязательно совпадает с реальным адресом обращения. Содержимое этого регистра действительно лишь при установленном бите BFSR.BFARVALID. Регистр BFAR может технически совпадать с регистром MMFAR, поскольку прерывания BusFault и MemManage не могут произойти одновременно. В такой ситуации, если после прерывания BusFault происходит прерывание MemManage, содержимое регистра BFAR изменяется и уже не отражает адрес, вызвавший прерывание BusFault. Произойдёт ли при этом сброс бита BFSR.BFARVALID, документация не сообщает. Поддержка режимов безопасности. Это поле не имеет отдельных версий для каждого из режимов. Если AIRCR.BFHFNMINS сброшен, доступ в небезопасном режиме невозможен (запись игнорируется, чтение возвращает нуль). Если реализация имеет совмещённые регистры BFAR и MMFAR, совмещаются BFAR и безопасная версия MMFAR, чтобы код небезопасного режима не мог получить содержимое BFAR через доступный ему MMFAR. Состояние после сброса не определено. |

В документации регистр BFAR описан как имеющий доступ на чтение и запись, однако логично предположить, что он доступен только на чтение, поскольку он хранит адрес, обращение к которому вызвало отказ, что устанавливается аппаратно.

Вспомогательный регистр состояния отказов AFSR[]

Адрес: E000ED3C.

Доступ: чтение/запись. Отдельных версий для разных режимов безопасности не имеет. Начиная с ARMv8.1-M, возможность записи в этот регистр отладчиком, если процессор не остановлен, определяется реализацией.

Наличие: формально отсутствует лишь в ARMv6-M, фактически — определяется реализацией.

Назначение разрядов этого регистра определяется реализацией.

Регистр AFSR в Cortex-M3 и Cortex-M4[]

Биты регистра AFSR в ядрах Cortex-M3 и Cortex-M4 устанавливаются, когда появляется единица на соответствующем входе шины вспомогательных отказов AUXFAULT (причины установки тех или иных линий этой шины определяются подключением процессорного ядра к остальной части вычислительной системы). Для сброса установленного бита программа должна записать единицу в соответствующую позицию этого регистра.

Появление единицы в каком-либо разряде AUXFAULT не вызывает прерывания, поэтому единственный способ узнать об изменении состояния его битов заключается в регулярном программно опросе.

Регистр управления доступом к сопроцессорам CPACR[]

Адрес: E000ED88.

Доступ: чтение/запись. При наличии расширения безопасности имеет отдельные версии дляр азных режимов. Начиная с ARMv8.1-M, возможность записи в этот регистр отладчиком, если процессор не остановлен, определяется реализацией.

Наличие: отсутствует в ARMv8-M без основного расширения и в ARMv6-M.

Каждое из двухбитовых полей этого регистра определяет возможность использования сопроцессора с соответствующим номером. Если такой сопроцессор отсутствует, соответствующее ему поле зарезервировано и всегда содержит значение 00.

Возможные значения поля управления доступом для имеющегося сопроцессора:

- 00 — доступ запрещён;

- 01 — разрешён доступ только привилегированному коду;

- 10 — зарезервировано;

- 11 — разрешён полный доступ.

Назначение и наличие сопроцессоров CP0–CP7 определяется реализацией. Наличие сопроцессоров CP8—CP15 также определяется реализацией, однако функции этих сопроцессоров определяются компанией ARM.

В настоящее время определено назначение лишь сопроцессоров CP11 и CP10: оба они на самом деле являются одним сопроцессором, реализующем FPU и MVE (последнее расширение может присутствовать в ARMv8-M). Реальное управление доступом к этому сопроцессору задаётся полем CP10; программа должна заносить в CP11 те же значения, что и в CP10, но не полагаться на содержимое поля CP11.

Состояние полей регистра CPACR после сброса определяется реализацией.

Регистр управления небезопасными доступами NSACR[]

Адрес: E000ED8C.

Доступ: При отсутствии расширения безопасности считывается как 00000CFF, запись невозможна. При наличии расширения безопасности имеется в единственном экземпляре и доступен безопасному коду для чтения и записи; небезопасный код доступа не имеет (считывается нуль, запись игнорируется). Начиная с ARMv8.1-M, возможность записи в этот регистр отладчиком, если процессор не остановлен, определяется реализацией.

Наличие: имеется только в ARMv8-M с основным расширением.

Каждый реализованный бит этого регистра соответствует одному из сопроцессоров. Когда бит равен нулю, небезопасный доступ к соответствующему сопроцессору запрещён, и при попытке такого обращения возникает прерывание UsageFault по отсутствию сопроцессора. Когда бит равен единице, доступ разрешён.

Состояние после сброса определяется реализацией.

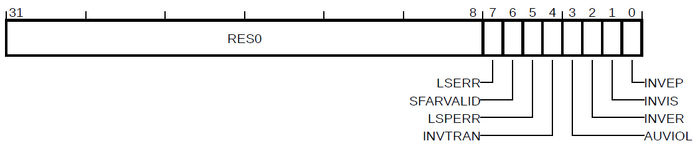

Регистр состояния прерывания SecureFault SFSR[]

Адрес: E000EDE4.

Доступ: чтение/запись; запись единицы очищает соответствующий бит. Отдельных версий для каждого режима безопасности этот регистр не имеет; доступ небезопасного кода невозможен (запись игнорируется, при считывании возвращается нуль). Начиная с ARMv8.1-M, возможность записи в этот регистр отладчиком, если процессор не остановлен, определяется реализацией.

Наличие: только ARMv8-M с основным расширением.

| Разряды | Доступ | Обозначение | Функция |

|---|---|---|---|

| Зарезервированы | |||

|

Установлен, если прерывание SecureFault возникло из-за при отложенной активации или деактивации состояния. При сбросе обнуляется. | |||

|

При сбросе обнуляется. | |||

|

Установлен, если прерывание SecureFault возникло из-за обнаружения нарушения SAU или IDAU при отложенном сохранении контекста FPU. При сбросе обнуляется. | |||

|

Установлен, если прерывание SecureFault возникло из-за перехода, не отмеченного как осуществляющего переход из безопасной в небезопасную память. При сбросе обнуляется. | |||

|

Установлен, если прерывание SecureFault возникло из-за попытки небезопасного доступа к безопасной части адресного пространства. Этот бит не устанавливается, если данное нарушение возникло при отложенном сохранении контекста FPU (см. бит LSPERR) или при выборке вектора прерывания. При сбросе обнуляется. | |||

|

Установлен, если прерывание SecureFault возникло из-за попытки возврата из прерывания в небезопасное состояние со сброшенным битом EXC_RETURN.DCRS или установленным битом EXC_RETURN.ES. При сбросе обнуляется. | |||

|

Установлен, если прерывание SecureFault возникло из-за попытки возврата из прерывания при неверном значении сигнатуры целостности в кадре стека. При сбросе обнуляется. | |||

|

Установлен, если прерывание SecureFault возникло из-за недопустимой попытки войти в безопасное состояние. При сбросе обнуляется. |

Регистр адреса прерывания SecureFault SFAR[]

Адрес: E000EDE8.

Доступ: чтение/запись. Отдельных версий для каждого режима безопасности этот регистр не имеет; доступ небезопасного кода невозможен (запись игнорируется, при считывании возвращается нуль). Начиная с ARMv8.1-M, возможность записи в этот регистр отладчиком, если процессор не остановлен, определяется реализацией.

Наличие: только ARMv8-M с основным расширением.

| Разряды | Доступ | Обозначение | Функция |

|---|---|---|---|

|

Адрес, при попытке обращения по которому возникло прерывание SecureFault. Содержимое этого регистра действительно лишь при установленном бите SFSR.SFARVALID. Регистр SFAR может технически совпадать с регистрами BFAR и MMFAR_S, поскольку прерывания SecureFault, BusFault и MemManage не могут произойти одновременно. В такой ситуации, если после прерывания SecureFault происходит прерывание BusFault или MemManage, содержимое регистра SFAR изменяется и уже не отражает адрес, вызвавший прерывание SecureFault. Произойдёт ли при этом сброс бита SFSR.SFARVALID, документация не сообщает. Состояние после сброса не определено. |